Escrito por: Ciro Gamboa

Revisado por: Holguer A. Becerra.

Se recomienda adquirir los conceptos expuestos en 2) Introducción antes de abordar este manual.

Objetivos:

- Describir el proceso de simulación en ModelSim, para diseños digitales implementados en Verilog.

- Usar el concepto de FSM (Finite State Machine), como metodología de diseño digital, orientado a la descripción de hardware.

Introducción a la simulación digital con ModelSim

ModelSim para el diseño digital

La importancia de la simulación

Como se conoce bien, la implementación de cualquier circuito complejo en la electrónica, conlleva un gran número de factores de riesgo, que influencian el comportamiento del mismo. Dentro de estos factores, destacan los errores humanos.

Tanto en la electrónica analógica como en la digital, con el paso del tiempo, se ha incrementado exponencialmente la complejidad de los circuitos, por lo que cualquier error, por pequeño que sea, puede dañar meses y hasta años de trabajo.

De allí surge la necesidad de la simulación, la cual ofrece innumerables herramientas para el diseño(dependiendo del caso) y respalda el funcionamiento de un circuito, antes de fabricarlo físicamente .

Simulación con ModelSim

Con respecto al diseño de electrónica digital, se enfatiza en la utilidad de las FPGAs y su práctico uso, por medio de lenguajes de descripción de hardware. La herramienta de simulación más usada para sistemas que involucran FPGAs es ModelSim, ya que puede ser usada con los lenguajes de descripción de hardware más comunes como Verilog o VHDL, así como su capacidad para trabajar de la mano con el software producido por las empresas desarrolladoras de FPGAs más importantes, tales como Xilinx o Altera.

Preparando el simulador

Para probar le funcionamiento del simulador, se usará el módulo divisor de frecuencia.

Se procede a abrir ModelSim

El software nos da una pequeña bienvenida, por ahora le damos "Close".

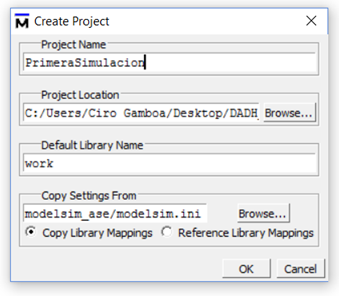

Tras estar dentro del simulador, se recurre a crear un nuevo proyecto, para guardar nuestros archivos de simulación, con lo que se le da un nombre al nuevo proyecto y se le asigna una ruta dentro del pc:

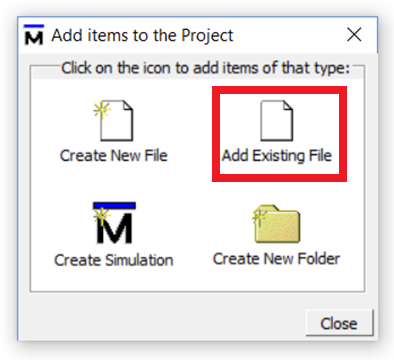

Una vez asignado el nombre a nuestro proyecto, automáticamente aparece una ventana, que nos facilita la inclusión de archivos dentro del proyecto, allí se tienen diferentes opciones, entre las cuales está, por ejemplo el crear archivos en lenguaje de descripción de hardware desde cero. En éste caso, seleccionamos la opción "Add Existing File", ya que el archivo que queremos probar, ya está escrito.

Procedemos a buscar el archivo del módulo que queremos simular, que en este caso es el del divisor de frecuencia planteado anteriormente. Tras abrirlo, le damos OK y posteriormente, cerramos la ventana de añadir archivos.

Una vez cargado el módulo a simular en nuestro proyecto, se puede evidenciar que éste tiene un símbolo de interrogación "?" referente a su estatus; es necesario que el simulador reconozca correctamente el módulo cargado, para poder leerlo sin problemas. Para ello, damos click sobre el módulo cargado y vamos a "Compile" en la barra de herramientas superior, en donde seleccionamos la opción "Compile Selected", cuya función es, como bien su nombre lo dice, compilar el módulo seleccionado. Tras hacer esto, se puede apreciar que el estatus del módulo cambia. Si aparece un chulo verde, significa que el módulo no tiene errores de sintaxis y está listo para ser usado; en caso contrario, sería necesario revisar el archivo.

Ahora se procede a iniciar la simulación. Se va a "Simulate" --> "Start Simulation". Luego, es necesario decir específicamente qué queremos simular, los archivos que subimos al proyecto, quedarán en la librería "work". Entramos allí y seleccionamos nuestro archivo.

Al tener el archivo listo para simular, la interfaz cambia; en este paso, debe lucir de la siguiente manera:

Concentrando la atención en la ventana azul de la derecha, nos fijamos en su esquina superior derecha en donde aparecen las entradas, salidas y señales internas, declaradas en nuestro módulo de divisor de frecuencia, le damos click al botón de la mitad, para hacer zoom.

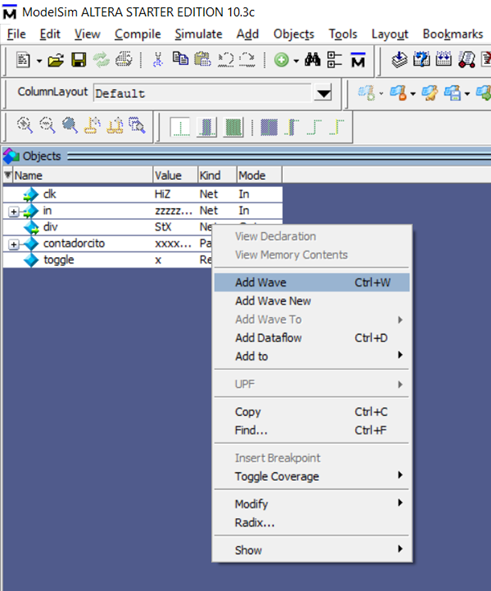

Ahora se seleccionan todos los parámetros del módulo y se les da click derecho ---> "Add Wave", ésto es para añadir la simulación por medio de gráficas.

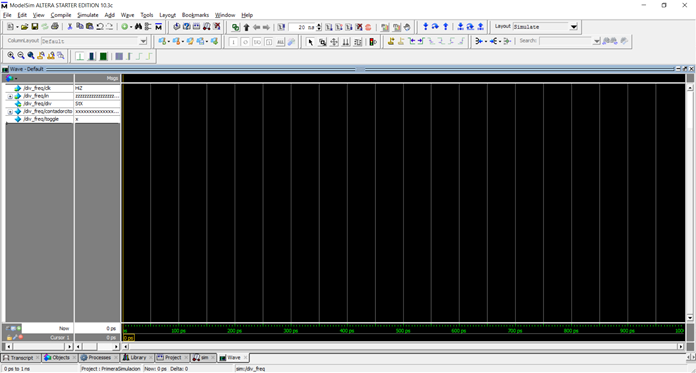

Tras "añadir ondas", el espacio de trabajo vuelve a cambiar y queda de la siguiente manera:

El modo de simulación por gráficas de onda, es una herramienta adicional en ModelSim. Todas las herramientas que se tienen abiertas, se muestran como pestañas en la parte inferior de la pantalla, por lo que si no le salió inmediatamente la pantalla tal y como se muestra en la figura anterior, ésta la encontrará en la pestaña "Wave".

Asignando valores a las señales

Con el fin de inducir valores en los parámetros que nos interesan, tenemos básicamente 3 opciones, que son "Force..", "NoForce" y "Clock..."; que se acomodan a las necesidades que tengamos. En el módulo del divisor de frecuencia, clk es el reloj de entrada, que en éste caso asumiremos que es de 50Mhz (T = 20ns), acudiendo a los relojes que se pueden usar directamente de la FPGA. Para asignar éste reloj a la señal como tal, en la simulación, vamos a /div_freq/clk y le damos click derecho. Posteriormente, seleccionamos "Clock...". Asignamos el periodo correspondiente y si queremos, podemos cuadrar parámetros como el duty cycle, el offset, entre otros.

Para señales asíncronas, es más conveniente usar "Force...". En el editor de señales "forzadas", podemos cambiar el nombre a la señal, añadir delays, pero lo más importante es asignarle un valor a la señal. Para este caso particular, de la señal de frecuencia de entrada, se le asignara un valor de 1. Este valor produce que la frecuencia de la señal de salida sea de 1/4 (un cuarto) de la frecuencia de la señal de entrada, que es 50MHz, para éste caso. (Ver ecuación del módulo de división de frecuencia en 2) Introducción ).

Para asignar el valor a la señal, se usa la misma nomenclatura que en Verilog. Para asignar el valor de 1 a una señal de 32 bits, se escriben primero el número de bits (32), seguido de ' (32') , luego el sistema numérico para representar el valor como tal (32'd) y por último el valor en si (32'd1).

El manejo del tiempo de simulación, es la base de una simulación exitosa en ModelSim, ya que de el depende la variación de todos los parámetros que nos interesan, actúa como si fuese "el reloj" del programa. En la casilla señalada en la siguiente imagen, se encuentra el tiempo de simulación estipulado. En este caso, serán 20ns que equivalen a un periodo del reloj de 50MHz. Los botones que están a la derecha de el tiempo de simulación, corresponden a "Run", "Continue run", "Run-all" y "Break". "Run" se encarga de simular durante el tiempo de simulación estipulado, en este caso, serían 20ns. "Continue run", simula hasta que le digamos cuando parar, lo cual se hace con "Break".

Cabe destacar que tras cada simulación dependiendo del tiempo escogido, se pueden recofigurar los parámetros del módulo, es decir, se pueden cambiar los relojes, forzar de nuevo las señales, etc.

Tras correr la simulación con "Run", obtenemos el siguiente resultado:

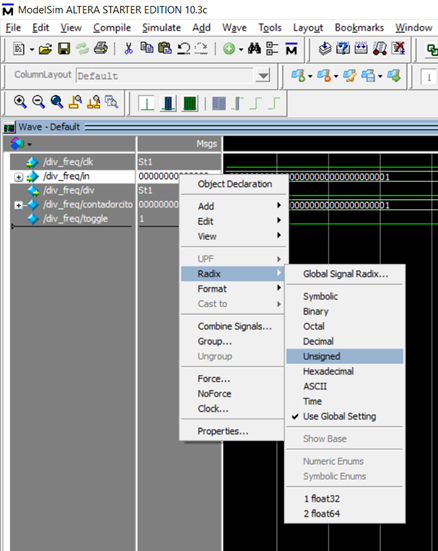

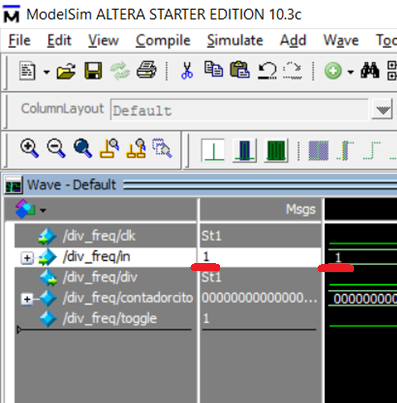

Como se puede evidenciar, no es muy claro lo que se pretende con éste resultado, empezando por los 32 bits representando tan solo un 1. Para corregir ello, se va a la señal cuyo valor queremos cambiar en cuanto a su visualización, le damos click derecho y y escogemos "Radix", allí escogemos el formato que más nos convenga, en este caso, la frecuencia de entrada es un valor constante en 1. Con "Unsigned" o "Decimal", funciona a la perfección.

Mejorando la apariencia de la simulación

Simulando por varios periodos de 20ns, o con simulación continua, aún no se logran identificar claramente las ondas, para ayudarnos con ello, damos click derecho sobre el fondo negro del simulador de ondas y seleccionamos "Zoom Full".

Con ello, ya tenemos una representación mucho más clara de cada onda, con defectos aún, pero va mejorando.

Por el momento, solo queremos observar la frecuencia de entrada, con respecto a la de salida, para identificar si ésta realmente la relación entre sus frecuencias es de 1/4. Por ello, eliminamos el resto de las ondas, que corresponden a las señales internas y a la frecuencia de entrada, ya que es tan solo una constante. Esto se hace dando click derecho a la señal que queremos eliminar, seleccionamos "Edit" --> "Delete".

Con ello, ya tenemos las señales que más nos interesan, pero aún falta algo más para que se vea un poco más estética la simulación, le daremos colores distintos a las ondas, ésto se puede lograr de la siguiente manera:

Damos click derecho a la señal de interés y vamos a "Properties...". Allí aparece una ventana en donde podemos cambiar diferentes propiedades de la onda correspondiente a la señal seleccionada. En "Wave Color", seleccionamos "Colors..." y allí escogemos el color de nuestra preferencia para la onda. Aceptamos los cambios y repetimos para las ondas restantes.

Finalmente obtenemos una simulación limpia y clara de nuestro divisor de frecuencia, en donde podemos apreciar que el reloj (clk) o frecuencia de entrada, cuya señal es la blanca, tiene un periodo 4 veces mayor, que la señal roja, que corresponde la frecuencia de salida. Con ello comprobamos que el módulo de división de frecuencia funciona bien y que la simulación resulta una herramienta con una utilidad enorme y en el caso de ModelSim, suprema mente fácil de usar.

Máquina de estados finitos (Finite state machine - FSM)

Conceptos base de FSM

Una FSM, es un modelo de computación usado para diseñar programas de computadora y circuitos de lógica secuencial.

Entre sus representaciones teóricas más comunes, se encuentra el diagrama de estados; que corresponde a un conjunto de círculos, en donde cada uno representa un estado y están interconectados por medio de flechas, que indican cual es el siguiente estado (y en algunos casos, cual es la salida del sistema), a partir de una entrada específica. Aquí hay un ejemplo de esa representación:

El diagrama de estados es una forma muy didáctica de representación de una máquina de estados, pero cuando ésta llega a ser muy grande, se pierde claridad en la información que esta provee, por lo que es apropiado, de la misma manera, el representar el comportamiento de una máquina de estados con su tabla de transiciones.

La tabla de transiciones de la FSM, presentada anteriormente, sería la siguiente:

|

Estado actual

|

Entrada

|

Salida

|

Siguiente estado

|

|

S0

|

0

|

0

|

S1

|

|

1

|

0

|

S0

|

|

S1

|

0

|

0

|

S1

|

|

1

|

0

|

S2

|

|

S2

|

0

|

0

|

S1

|

|

1

|

0

|

S3

|

|

S3

|

0

|

1

|

S1

|

|

1

|

0

|

S0

|

Entre las máquinas de estado, las que nos interesan para fines de este curso, son las que tienen salida. Éstas a su vez, se dividen en dos tipos de máquina: tipo Mealy y tipo Moore. Con el enfoque de circuitos digitales, decímos que:

Máquina de Moore

En este tipo de FSM, la salida del circuito, solo depende del estado en que se encuentra la máquina, no de sus entradas. Los circuitos que siguen éste patrón, se ven representados por el siguiente modelo:

El diagrama de estados correspondiente a la FSM de tipo Moore, se presenta de la siguiente manera:

En donde Ei es el nombre del estado,

Zi es la salida que corresponde a dicho estado,

y Xi la entrada que provoca el salto a otro estado.

Máquina de Mealy

En este tipo de FSM, la salida del circuito, depende tanto del estado de la máquina, como de sus entradas. Los circuitos que siguen éste patrón, se ven representados por el siguiente modelo:

En este diagrama se puede apreciar la relación directa de la entrada, con la salida.

Con respecto a los diagramas de estados, correspondientes a este tipo de FSM, se tiene que:

Igual que en el caso anterior, Ei es el nombre del estado,

Xi es la entrada que provoca el salto a otro estado. La diferencia radica en

Zi, que es la salida que corresponde a dicho estado (Ei), cuando la entrada es Xi.

Cabe destacar que una consecuencia importante es que en una máquina de Moore las salidas son síncronas, es decir, sólo cambian en los flancos de reloj. En cambio en las máquinas de Mealy cambiarán con las entradas, es decir, en cualquier instante.

Diseño digital de una FSM en la FPGA DE0-NANO SoC, con Verilog y ModelSim

Planteamiento teórico

Con el fin de poner en práctica el concepto de FSM, que será ampliamente usado en sesiones posteriores, se propone una secuencia de combinaciones de bits, que deberan ser visualizadas en los leds de la FPGA. La secuencia es la siguiente:

10101010 ---> 01010101 ---> 10000001 ---> 01000010 ---> 00100100 ---> 00011000

Una vez finalizada la secuencia, ésta deberá iniciar de nuevo.

Para hacer el proceso más intuitivo, se le asignan nombres a cada combinación o cada estado. Cada una tendrá una asignación diferente, ya que no hay secuencias repetidas.

IDLE: 10101010

STATE1: 01010101

STATE2: 10000001

STATE3: 01000010

STATE4: 00100100

FINISH: 00011000

Adicionalmente, para afianzar el uso de las FSM y aumentar un poco el grado de dificultad, se proponen estas condiciones:

- Para pasar de IDLE a STATE1, será necesario que una bandera "start" sea activada.

- Para pasar de STATE1 a STATE2, un switch de la FPGA, deberá cambiar de estado.

- Para terminar el ciclo de la FSM y volver al estado IDLE, se deberá permanecer en el estado FINISH durante 15 segundos.

El diagrama de estados que representa esta situación, luce de esta manera:

Las flechas que no tienen condición, simbolizan un paso inmediato al siguiente estado. Cabe destacar que esta FSM es de tipo Moore, ya que las salidas dependen únicamente del estado en que se encuentra la máquina; las entradas solo sirven como parámetro de transición entre los estados y no afectan a la salida directamente.

Codificación de el módulo FSM

Con estas herramientas, ya estamos listos para la implementación en código de esta FSM.

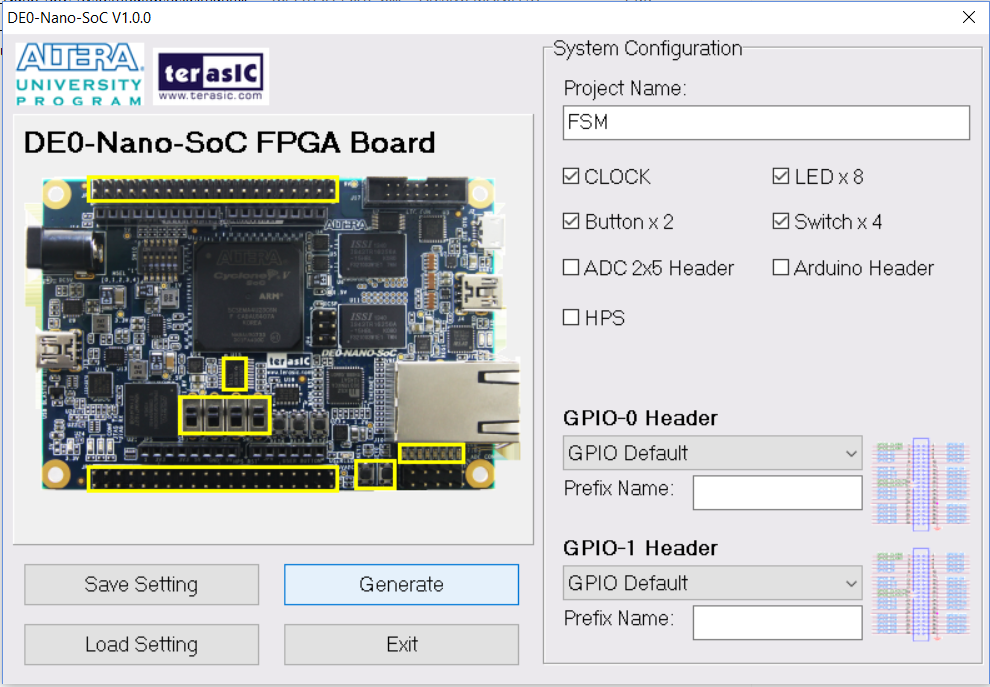

Procedemos a crear un nuevo proyecto con el SystemBuilder, en donde usaremos los switches y los leds de la FPGA:

Tras tener nuestra plantilla principal, en donde se conectarán los módulos que necesitemos para cumplir con los requerimientos prácticos de la FSM planteada, se procede a crear el módulo correspondiente al funcionamiento de la máquina de estados como tal.

El módulo encargado del funcionamiento de la FSM, se bautizó como fsm_secuencia. Estas son las entradas y salidas definidas para éste módulo.

Naturalmente se hace necesario el uso de un reloj (clk), ya que éste determina la velocidad de la máquina como tal. Además de clk, se declaran como entradas start y sw_0, cumpliendo con los requisitos de la FSM planteada.

Como salidas se tiene finish e idle; ésto con el propósito de monitoriar el momento los estados más críticos de nuestra FSM. La salida de 8 bits correspondiente a los leds, en donde se visualizará el resultado, es de vital importancia.

Luego, se crea una serie de parámetros clave, para la definición de los estados, de la siguiente manera:

Con la palabra reservada localparam, se declaran contantes útiles para el desarrollo del código. Éstas se asemejan a los macros, en lenguajes de programación de alto nivel.

Como se puede apreciar, se crea un localparam para cada estado dentro de la FSM definida, en este caso, usaremos 8 bits, en donde tomamos el más significativo, para saber en que estado se encuentra finish. De la misma manera el segundo bit más significativo, se usa para saber sobre idle. La asignación directa, se explica más adelante.

Los guiones bajos que hay entre los valores de los bits, no son motivo de preocupación; el compilador los ignora, por lo que son una buena herramienta para hacer el código más legible e intuitivo.

Los 6 bits restantes, son los los que caracterizan a cada estado en particular. El patrón de los bits, sigue una metodología llamada one hot, en la cual, para cada estado, se tienen tantos bits como estados tenga la FSM, y solo hay un bit en alto. Existen otras metodologías para éste tipo de asignaciones, tales como en código Grey, o la contraparte de one hot, llamada one cold, en donde todos los bits son altos, exceptuado 1. Por ejemplo 11110, 11101,11011,10111,01111. En general, cualquier valor puede ser asignado a los estados de la FSM para diferenciarlos.

One hot es muy apropiado para las FSM implementadas en FPGAs, ya que una FSM One-hot, no necesita un decodificador, por que la máquina de estado esta en el n-avo estado, si y solo si el n-avo bit está en alto. Por cada estado, se crea un flip-flop, por lo que los estados de la máquina se pueden ver representados como una serie de flip-flops en cascada. Además la detección del estado es muy económica en términos de procesamiento, por que solo se requiere el acceso a un flip-flop; de la misma manera, es muy sencillo detectar estados erróneos con ésta metodología. One hot usa más flip-flops que otros métodos, lo cual es una desventaja, pero implementado en la FPGA, no tiene problema ya que ésta contiene una enorme cantidad de ellos.

Ahora, creamos los siguientes registros y asignaciones:

El registro de estados state, es el que usaremos para movernos entre los estados previamente definidos de nuestra FSM, a partir de éste registro, se tomarán las decisiones respectivas de cada estado y su salida correspondiente. Tiene 8 bits, al igual que los localparam definidos anteriormente.

El registro conteo, tiene 4 bits, ya que queremos un contador que llegue hasta 15, para cumplir con el requerimiento propuesto para el estado FINISH.

Se le asigna el MSB y el segundo más significativo al las salidas finish e idle, por los motivos mencionados previamente.

Prosiguiendo con la definición del módulo, se le asigna a la salida por excelencia, los leds, los estados que requeridos, aprovechando la sintaxis de Verilog, que permite hacer una comparación directa de múltiples casos y dependiendo del caso, se le asigna un valor a la salida. (state[7:0] == IDLE)? 8'b10101010, significa, "si el estado (state) es igual a IDLE, el bus de leds, toma el valor de 10101010.

Tras tener todos las asignaciones del módulo listas, proseguimos con la lógica secuencial, que siempre va dentro de un bloque always. Se usara el flanco de subida del reloj de entrada, como referencia para el avance de secuencial de la FSM.

Se establece un case, dentro del bloque always, que se encarga de multiplexar la acción a tomar a partir del valor de state, el cual es comparado con los localparam que fueron definidos con anterioridad (IDLE, STATE1... FINISH).

En todos los estados, se asigna el valor de cero a conteo, ya que solo lo vamos a usar en FINISH. Hay que hacerlo, porque al dejarlo sin un valor fijo, el compilador podría asignarle un valor que considere 'optimo' para la posterior descripción de hardware.

En IDLE, se incluye la condición requerida, en la cual se necesita que start sea igual a 1, para poder pasar a STATE1.

De manera similar que en IDLE, el paso de STATE1 a STATE2, depende del estado de sw_0, en donde pasaría a STATE2, con un valor de 1 y se quedaría en STATE1, con un valor de 0.

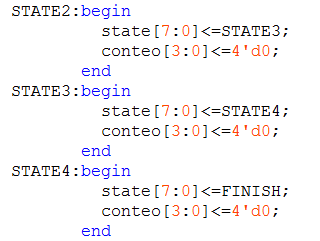

Prosiguiendo con la lógica secuencial de nuestra FSM, se establecen STATE2, STATE3 y STATE4.

Estos estados, son estados de transición similares sin ninguna condición específica.

Estos estados tan solo cambian el valor de la salida.

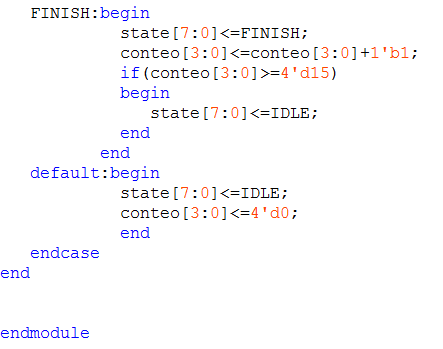

Por último, se cumple la el requisito del estado FINISH, en cuanto al conteo menor a 15, ya que la FSM permanecerá en éste estado, hasta que conteo, llegue a un valor de 15; mientras esa condición no se cumpla, a conteo se le suma de a un bit. Como todo esto sucede con cada flanco de reloj de clk, si se tiene que clk es de 1Hz, el conteo duraría 15 segundos. Cuando conteo es 15, el siguiente estado es IDLE; de ésta manera se repite el ciclo de la FSM. Si state llega a tener un valor que no corresponde a ninguno de los estados definidos, la FSM va a IDLE.

Con ésto hemos terminado del módulo de la máquina de estados deseada.

////Titulo de modulos adicionales o algo asi...

La máquina de estados diseñada, necesita de un par de módulos adicionales, para tener un comportamiento autónomo y limpio. Ya que queremos que los leds cambien de estado, según lo planteado anteriormente, de manera automática, el clk incluido, deberá provenir de la FPGA; por lo que un divisor de frecuencia se hace necesario. De la misma forma, como se pretende manejar las entradas asíncronas (sw_0 y start) con switches, o pulsadores se podrían presentan problemas de sincronización de datos, relativos a la meta estabilidad por lo que surge la necesidad de de usar el módulo syncro, desarrollado en prácticas pasadas.(Ver

2) Introducción) Los módulos a usar, se reflejan en la imagen de la izquierda.

Para un correcto funcionamiento se propone conectar los módulos de la siguiente manera:

Se propone el uso de la señal de inicio de la FSM (start), con un pulsador, mientras que sw_0 con un Switch. Esto con el fin de usar diferentes interfaces ofrecidas por la FPGA.

El valor de 24999999 en el módulo del divisor de frecuencia, hace que éste genere un valor de 1Hz; el reloj de 1Hz, será el reloj de la FSM y servirá como referencia para la sincronización de las señales de entrada.

Teniendo el diseño en mente,ya se procede a hacer la instanciación de los módulos, en el módulo principal 'FSM'.

Primero, creamos algunos cables que nos permitan unir nuestros módulos de manera efectiva.

Al cable que sale del módulo div_freq, lo llamamos clk_1hz. (Porque será un reloj de 1Hz).

Al cable que va entre syncro1 y FSM, lo llamamos sync_start.

Al cable que va entre syncro2 y FSM, lo llamamos sync_switch.

He aquí, por fin, nuestra primera instancia. Se trata de la del bien conocido divisor de frecuencia. Su reloj de entrada, será el de 50Mz, interno de la FPGA. Su entrada 'in', tiene el valor de 24999999 (para 1Hz de salida) y su salida va al cable que recién fue creado, clk_1hz.

La siguiente instancia, corresponde a syncro1. Se le asigna a la entrada asíncrona del módulo, el pulsador KEY[0], que hace alusión a la señal de start de la FSM. La señal que provee éste pulsador, se sincroniza con el reloj de 1Hz, que es el propio de la FSM planteada, por ello, se le asigna clk_1hz. La señal sincronizada de salida, va al cable sync_start.

Ahora, se instancia el segundo módulo de sincronización syncro2. A su entrada asíncrona, se conecta el Switch 0 de la FPGA(SW[0]), funciona con el mismo reloj que syncro1 1 FSM, por ellos también se conecta a clk_1hz. Su salida sincronizada, va a sync_switch.

Por último, se instancia el módulo de nuestra máquina de estados finitos, al cual llamamos fsm_secuencia. El reloj de entrada, que es el mismo en el que se basa la máquina de estados diseñada, es de 1Hz, y viene del cable clk_1hz, que proviene del módulo de división de frecuencia. Las señales start y sw_0, están conectadas a las salidas de los sincronizadores, cuyas entradas son un pulsador para start y un switch para sw_0 respectivamente. Las salidas son finish, idle y por supuesto, los leds. En la FPGA, solo veremos los leds en acción.

Teniendo ya el código necesario para nuestra FSM, miramos el RTL, para comparar con nuestro sistema propuesto:

Simulación e implementación directa en la FPGA

En cuanto a diseño superficial, los módulos están bien conectados. Ahora pasamos a la etapa de simulación, para comprobar el funcionamiento de la FSM.

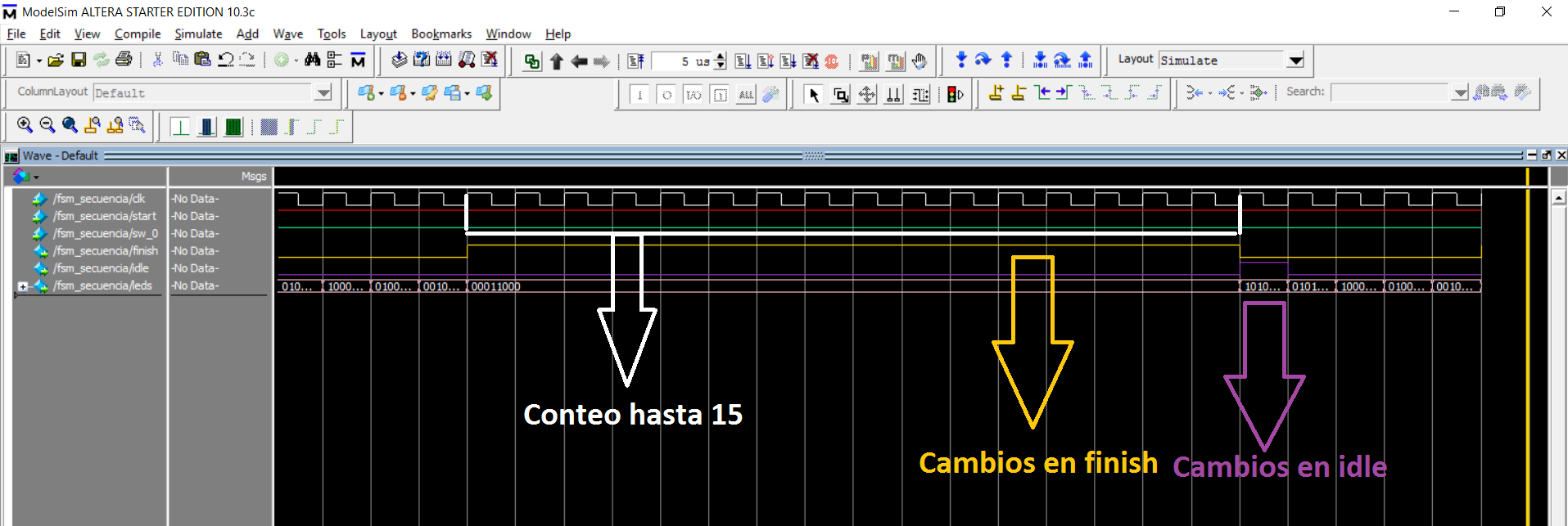

Para llegar a la simulación, tal y como se tiene en la siguiente imagen, fue necesario seguir todos los pasos de simulación descritos en la parte superior de ésta guía. Luego, se eliminaron las constantes de los estados (los localparam) y las variables internas, para solo dejar entradas y salidas. Se puso un reloj de 1MHz (T = 1us) y se forzaron las entradas sw_0 y start a cero. Como se puede apreciar, la salida que corresponde a los leds, inicia con un valor de 10101010, que es el valor de salida para el estado IDLE. Ya que no se ha cumplido la condición de que start sea igual a 1, la salida idle, se mantiene en alto.

Para proseguir con la simulación, se procede a forzar la entrada start a 1, ésto permitirá que la FSM, pase de IDLE a STATE1, cuya salida es 01010101. En el momento en que se produce éste cambio, la salida idle, pasa a ser cero. Se simula por más periodos, 5us es un buen valor para ver los cambios en la FSM.

Ahora, para poder salir del estado STATE1, es necesario que sw_0 tenga un valor de 1. Se le asigna un valor de 1 a ésta entrada. Acto seguido, como se observa en la siguiente imagen, la FSM sale de STATE1 y pasa a STATE2, tras otro periodo del reloj, a STATE3 y por último a FINISH (todos los pasos en flanco de subida del reloj de la FSM). La salida finish, se pone en alto.

Tras haber llegado al estado FINISH, con un valor asignado de 00011000, la FSM se queda por 15 ciclos de reloj (el reloj debe ser de 1Hz, si queremos que sean 15 segundos) en éste estado; durante ese tiempo, la salida finish se mantiene en alto. Pasados los 15 ciclos de reloj, la FSM vuelve a iniciar desde IDLE, pero continúa, ya que ambas condiciones, la de start y la de sw_0, ya se cumplieron; por lo que la salida idle, se mantiene en alto durante un periodo de reloj, luego la FSM, pasa por el resto de estados, como se puede apreciar en la siguiente toma.

Ya que dejamos start y sw_0, con el valor en alto, la FSM no tiene ninguna condición que impida que se repita y se repita. Simulamos por mucho más tiempo y le damos Zoom Full, para ver el panorama completo de la simulación, se puede ver que no hay sincronía al principio de la simulación, porque aún no estaban activas las entradas. Pero tras activarlas, el sistema entra en un loop, generando las ondas que se ven a continuación, para las salidas idle, y finish y generando el patrón de la máquina de estados planteada teóricamente.

Con esta simulación, se puede tener la certeza de que la FSM funcionará en la FPGA; una vez más se evidencia la importancia de la simulación en el diseño digital.

El resultado final, de la FSM implementada en la FPGA, se ve en el siguiente video:

Para continuar con el tema, se recomienda visitar las subpaginas de ésta sección o continuar con 4) IP Cores y Sync .