CISC

|

Complex Instruction Set Computing

|

RISC

|

Reduced Instruction Set Computing

A RISC processor has a few fixed size instructions, a lot of general purpose registers but a few addresing modes. They have a simpler control unit with a smaller circuit area which leads to high speed execution instruction.

|

|

Instruction [Label] : [Operation] [Rd], [Rs], [Rt], #[Imm/Dir] ;[Comment] Examples beq rg1, rg0, #16 ;Branch to address 16 if rg1 and rg0 are equal lw rg3, r0, #0 ;Load word in rg3 to the address r0+0 inc op ;Increment the Ouput Port Register

Control Register

|

Instructions Set

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

RISCKER Source

|

A RISC processor instruction set and organization is designed so that it represents this architecture’s characteristics, such as:

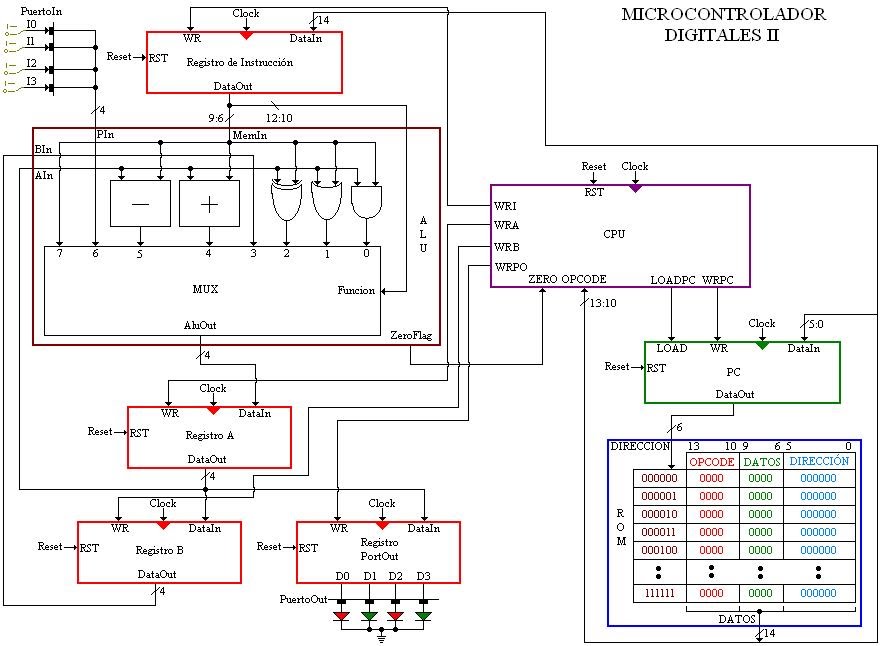

The processor's structure is similar to the Multi-cycle MIPS described by Patterson and Hennessy in order to facilitate the change between this system and a commercial MIPS-based processor in terms of code compatibility and structural behavior.

Along with the individual files there is an Archive containing the latest version of the full system.

For a Debugging-Compatible version of this processor go to RISCKER Observer.

|

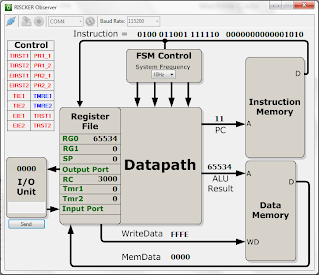

RISCKER Observer

|

This is a Debugging-Compatible hardware version of the RISCKER processor. It includes the necessary modules to create a serial connection through a UART protocol between the processor and the Observer tool in the X-ISCKER IDE software.

To download the latest version of all Verilog files use the *.zip Archive.

A Project *.qar (Quartus Archive) is provided for implementation in Terasic's DE0-Nano Development Board.

You can find the UART module on verilog here: Download UART Module

|

Applications

|

This is a space available for code applications created for the RISCKER processor. This includes: Program examples, Libraries, Macros, etc.

|

|

Instruction [Label]: [Operation] [Operand],[Addressing Mode] ;[Comment]

Examples

ADDA #10, IX ;Add ACCA with Memory[IX+10]

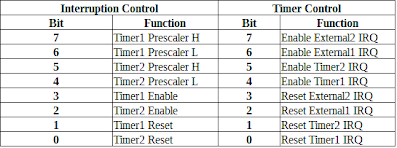

Control Registers Bits

|

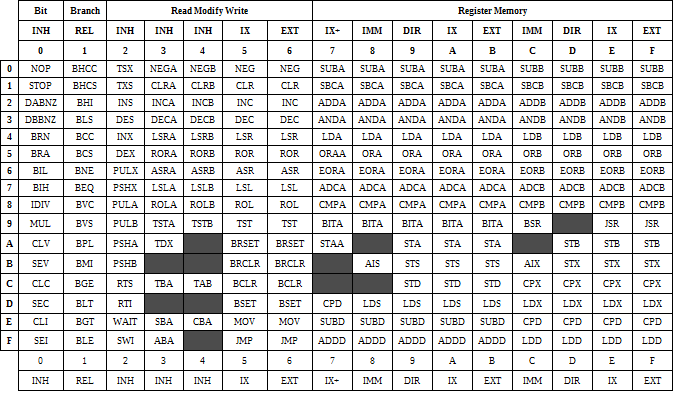

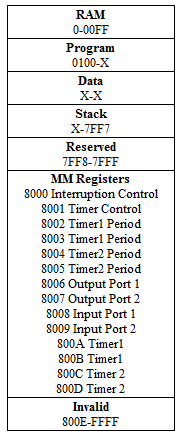

Instructions Map Memory Map |

CISCKER Source

|

This CISC processor is based on the instruction set of the Motorola (now Freescale) HC08 and HC11 series which symbolizes the characteristics of CISC architecture, with features like:

Along with the individual files there is an Archive containing the latest version of the full system.

For a Debugging-Compatible version of this processor go to CISCKER Observer.

|

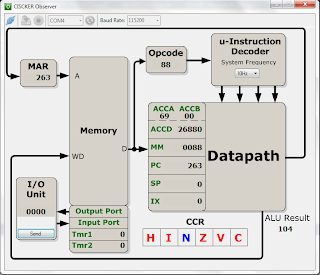

CISCKER Observer

|

This is a Debugging-Compatible hardware version of the CISCKER processor. It includes the necessary modules to create a serial connection through UART protocol between the Processor and the Observer tool in the X-ISCKER IDE software.

To download the latest version of all Verilog files use the *.zip Archive.

A Project *.qar (Quartus Archive) is provided for implementation in Terasic's DE0-Nano Development Board.

You can find the UART module on verilog here: Download UART Module

|

This is a space available for code applications created for the CISCKER processor. This includes: Program examples, Libraries, Macros, etc

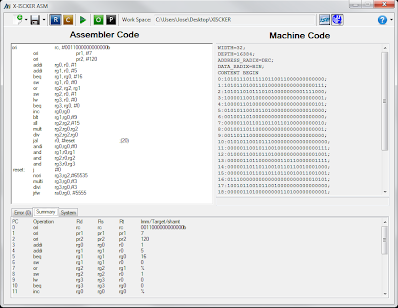

An IDE (Integrated Development Environment) is a must-have tool for software development. It must be capable of providing the user with assembling, programming and debugging tools in order to develop and test any software project for a given hardware.

Documentation

|

Apart from the overview given in this website, this section provides the Datasheets and User Manuals necessary for the implementation of the XISCKER Platform.

Note: Documentation is only available in Spanish to this date. We are working on the translation.

https://biblioteca.bucaramanga.upb.edu.co/application/index/material/24051 |

- Acquiring the processor HW

- Download the Quartus Archive (*.qar) according to the processor you want to use.

- Extract the *.qar contents in a folder with a Quartus-compatible path (no spaces or special characters)

- Open the Quartus Project (*.qpf)

- Compile the design and program your FPGA.

- Acquiring the SW

- X-ISCKER IDE's latest version is in the X-ISCKER IDE tab of this website.

- Download the latest version of the Installer *.zip

- Extract the *.zip

- Install on any Windows PC by double-clicking the "setup" file

- Requires .NET and a serial COM connection (VCOM USB is recommended through a Serial-USB converter)

- Execute the X-ISCKER IDE

- If it is the first time, select a workspace folder.

- Select the architecture.

- Write the assembly code on the left text box (use the proper syntax for each architecture).

- Save the Assembly File for future use.

- Click on “Run” (F5), To generate the memory file.

- You can check the summary tap for more information on the assembly process.

- Save the memory file on the Quartus project folder.

- Click on “Programmer” (F7).

- Select the bin path.

- Select the family device.

- Select the driver cable for Altera.

- Select the path of the project with the processor.

- On Altera: select the*.qpf file

- On Xilinx: select the top module (Verilog o VHDL).

- Click on “Program”

Prof. Alonso de Jesus Retamoso Llamas

Alfredo Gualdrón: agualdro [at] gmail.com